[ad_1]

Forward-looking: Very few electronic devices used here on Earth can survive when they leave the planet’s comfortable atmosphere. Processors, in particular, must be designed to withstand the harsh conditions of outer space, including radiation and near-absolute zero temperatures. It appears that RISC-V could help address this challenge.

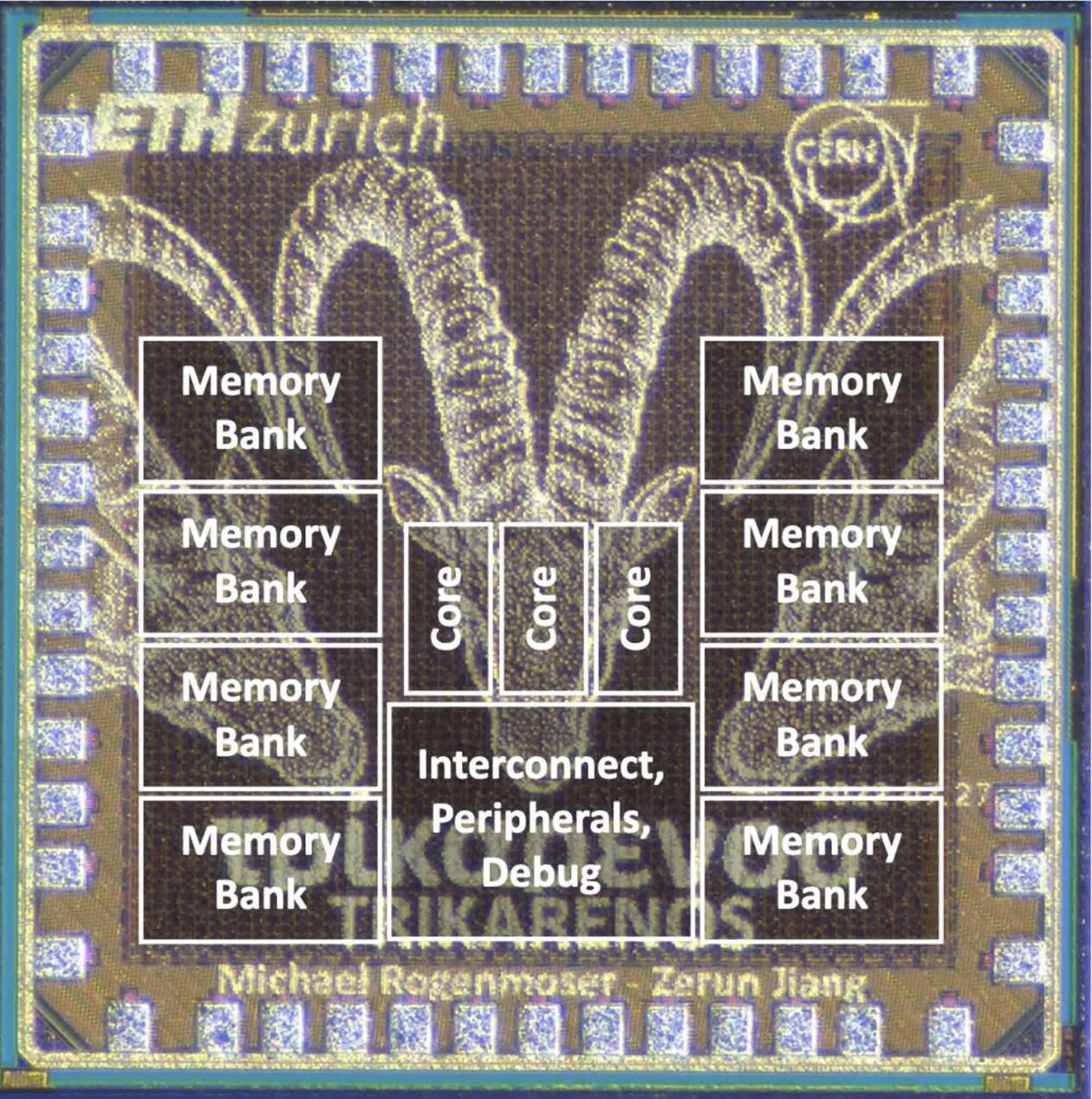

Researchers at the Swiss public university ETH Zurich have developed Trikarenos, a RISC-V-based microcontroller designed to operate reliably in harsh environments like space. Trikarenos can withstand radiation-induced single event upsets (SEUs), which are changes in the state of a micro-electronic device caused by a single ionizing particle. Additionally, it can deliver performance levels comparable to traditional “space chips” while consuming only a fraction of the same energy budget.

Common countermeasures to space conditions usually rely on proprietary, radiation-hardened technologies, low-density manufacturing nodes, and extensive replication, as explained by the researchers. These factors contribute to high costs and low levels of performance and efficiency. Trikarenos aims to address these challenges with a 32-bit RISC-V CPU architecture and “advanced” 28nm manufacturing technology provided by TSMC.

The 28nm node has demonstrated resilience to the “damaging effects” of radiation-induced SEU events, according to the researchers, and it offers unprecedented levels of efficiency compared to previous designs. Trikarenos utilizes the ultra-low power PULPissimo microcontroller architecture, which is open source, just like the RISC-V CPU architecture.

The chip incorporates three RISC-V-based Ibex computing cores, each clocked at speeds of up to 270 MHz, and they are supplied with data by eight SRAM banks, each with 256 KB of memory. These three cores operate in a “triple-core lockstep” configuration, where each core performs the same operation simultaneously. In the event of an SEU event corrupting one of the cores, a vote similar to the one depicted in Minority Report would determine the correct operation output.

Other architectural elements designed to enhance radiation tolerance include integrated redundancy, error-correcting memory banks, and a “memory scrubber” that continuously reads each memory address to correct any correctable errors. Additionally, the three Ibex cores are physically separated by a 20-micrometer gap around each core.

The three-core design offers increased fault tolerance but may impact the potential performance of the controller. Nevertheless, the design appears capable of delivering performance levels comparable to the PowerPC-based RAD750 chip, which has been in use for two decades and is still employed by major space agencies for their most complex missions, such as the James Webb Space Telescope. In the coming years, NASA intends to replace RAD750 with a high-performance RISC-V CPU designed by SiFive.

In comparison to RAD750, which consumes five watts of power, Trikarenos can achieve the same computing results with just 15.7 milliwatts, making it advantageous for energy-constrained missions like CubeSat satellite launches. If extreme reliability is not a requirement, the three cores can operate in parallel, providing 300 percent the performance of a triple-core lockstep design.

[ad_2]